# МХ•СЛМ, INC. MiXed Signal ICs

**DATA BULLETIN**

# **MX809**

## 1200bps MSK Modem

## PRELIMINARY INFORMATION

#### **Features**

- Half-Duplex 1200bps MSK Modem operating under C-BUS control

- Software Selectable Checksum Generation and Error Checking in accordance with MPT1327

- Low Power Operation

- Member of DBS800 Family (C-BUS Compatible)

The MX809 is an intelligent, half-duplex 1200-baud MSK Modem, which operates under C-BUS control. This modem provides software selectable checksum generation and error checking in accordance with MPT1327.

#### In TX Mode the MX809 will:

- 1. a) Accept from the host and transmit 8-bit bytes of data as instructed (preamble, sync, address, and data), or

- b) Internally calculate and inset a 2 byte checksum based on the preceding 6 bytes f data, or

- c) Disable the internal checksum generator and continuously transmit the data supplied.

- 2. Transmit 1 hang-bit and go to TX idle when all loaded data bytes have been transmitted.

## In RX Mode the MX809 will:

- 1. Detect and carry out bit synchronization within 16 bits.

- Search and detect the user-programmed Sync (or its opposite logic sense) Word and carry out frame synchronization. Data will then be output in 8-bit bytes via the RX Data Buffer.

- b) Use the received checksum to calculate the presence of any errors, setting the Status Register accordingly.

- Make the incoming data directly available via the RX Data Buffer (RX Freeformat), overriding the synchronization requirements.

RX input timing is achieved by recovering an RX clock from the incoming data stream. Output tones are timed to the internally generated TX clock. Filter, register clocks, and transmit MSK tone frequencies are derived internally from the external Xtal or clock pulse input.

A 4.032MHz Xtal or clock input is required for compliance with the MPT1327 Signaling Specification. Note: All information contained in this data bulletin is specified using a 4.032MHz Xtal, 1200bps baud rate, with Mark and Space frequencies of 1200Hz and 1800Hz. The MX809 has a non-committed amplifier on-chip for general applications in the DBS 800 series.

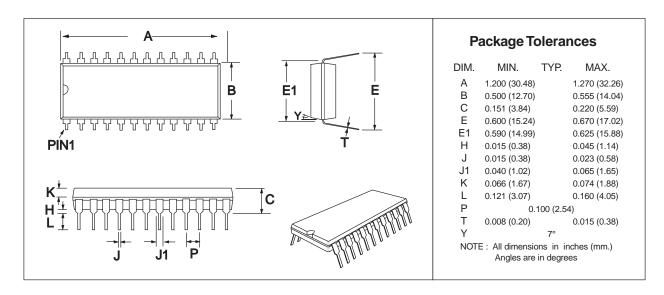

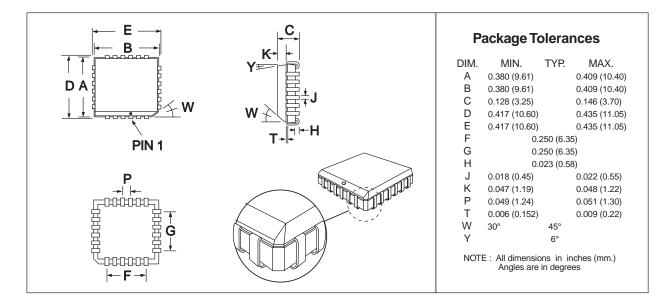

The MX809 may be used with a 5.0V power supply and is available in the following packages: 24-pin PLCC (MX809LH), and 24-pin CERDIP (MX809J).

## **Contents**

| 2 Signal List 3 External Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Se | ection                                       | Page |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------------------------------------------|------|

| 2 Signal List 3 External Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1  | Block Diagram                                | 3    |

| 4 General Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2  | Signal List                                  | 4    |

| 4 General Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3  | External Components                          | 6    |

| 5 Controlling Protocol 5.1 Address/Commands 5.2 Address Select 5.3 Write to Control Register 5.4 RX Data buffer "Read RX Data Buffer" 5.5 TX Data Buffer "Write to TX Data Buffer" 5.6 SYNC Program "Write to SYNC Program" 5.7 Read Status Register 5.8 Interrupt Request 5.9 General Reset 6 Application 6.1 Checksum Generation and Checking 6.1.1 Generation 6.1.2 Checking 6.2 Modem Performance 6.3 Modem Timing Information 6.4 TX Timing 6.4.1 TX More Than One Message, SYNC Before Every Message, TX Check-2 TX More Than One Message, TX Checksum Not Enabled 6.4.1 TX One Message, TX Checksum Enabled 6.4.4 TX One Message, TX Checksum Not Enabled 6.5 RX Timing 6.5.1 RX SYNC/SYNC Required Before Every Message, Rx Checksum Information 6.5.2 RX Additional Data Follows Initial Address (6 Data & 2 Checksum Benabled 7 Performance Specifications 7.1 Electrical Specifications 7.1 Electrical Specifications 7.1.1 Absolute Maximum Limits 7.1.2 Operating Limits 7.1.3 Operating Characteristics 7.1.4 Timing | 4  | General Description                          |      |

| 5.1 Address/Commands 5.2 Address Select 5.3 Write to Control Register 5.4 RX Data buffer "Read RX Data Buffer" 5.5 TX Data Buffer "Write to TX Data Buffer" 5.6 SYNC Program "Write to SYNC Program" 5.7 Read Status Register 5.8 Interrupt Request 5.9 General Reset 6 Application 6.1 Checksum Generation and Checking 6.1.1 Generation 6.1.2 Checking 6.2 Modem Performance 6.3 Modem Timing Information 6.4 TX Timing 6.4.1 TX More Than One Message, SYNC Before Every Message, TX Check-2 TX More Than One Message, TX Checksum Not Enabled 6.4.3 TX One Message, TX Checksum Not Enabled 6.4.4 TX One Message, TX Checksum Not Enabled 6.5 RX Timing 6.5.1 RX SYNC/SYNC Required Before Every Message, Rx Checksum I 6.5.2 RX Additional Data Follows Initial Address (6 Data & 2 Checksum Benabled 7 Performance Specifications 7.1 Electrical Specifications 7.1.1 Absolute Maximum Limits 7.1.2 Operating Limits 7.1.3 Operating Characteristics 7.1.4 Timing                                                            |    | ·                                            |      |

| 5.2 Address Select 5.3 Write to Control Register 5.4 RX Data buffer "Read RX Data Buffer" 5.5 TX Data Buffer "Write to TX Data Buffer" 5.6 SYNC Program "Write to SYNC Program" 5.7 Read Status Register 5.8 Interrupt Request 5.9 General Reset 6 Application 6.1 Checksum Generation and Checking 6.1.1 Generation 6.1.2 Checking 6.2 Modem Performance 6.3 Modem Timing Information 6.4 TX Timing 6.4.1 TX More Than One Message, SYNC Before Every Message, TX Check-2 TX More Than One Message, TX Checksum Not Enabled 6.4.3 TX One Message, TX Checksum Not Enabled 6.5 RX Timing 6.5.1 RX SYNC/SYNC Required Before Every Message, Rx Checksum I 6.5.2 RX Additional Data Follows Initial Address (6 Data & 2 Checksum Benabled 7 Performance Specifications 7.1 Electrical Specifications 7.1.1 Absolute Maximum Limits 7.1.2 Operating Characteristics 7.1.4 Timing                                                                                                                                                      | •  | •                                            |      |

| 5.3 Write to Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |                                              |      |

| 5.4 RX Data buffer "Read RX Data Buffer" 5.5 TX Data Buffer "Write to TX Data Buffer" 5.6 SYNC Program "Write to SYNC Program" 5.7 Read Status Register 5.8 Interrupt Request 5.9 General Reset 6 Application 6.1 Checksum Generation and Checking 6.1.1 Generation 6.1.2 Checking 6.2 Modem Performance 6.3 Modem Timing Information 6.4 TX Timing 6.4.1 TX More Than One Message, SYNC Before Every Message, TX Checked 6.4.2 TX More Than One Message, TX Checksum Not Enabled 6.4.3 TX One Message, TX Checksum Not Enabled 6.4.4 TX One Message, TX Checksum Not Enabled 6.5 RX Timing 6.5.1 RX SYNC/SYNC Required Before Every Message, Rx Checksum Info. 6.5.2 RX Additional Data Follows Initial Address (6 Data & 2 Checksum Benabled 7 Performance Specifications 7.1 Electrical Specifications 7.1.1 Absolute Maximum Limits 7.1.2 Operating Limits 7.1.3 Operating Characteristics 7.1.4 Timing                                                                                                                        |    |                                              |      |

| 5.6 SYNC Program "Write to SYNC Program" 5.7 Read Status Register 5.8 Interrupt Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | Ç                                            |      |

| 5.7 Read Status Register 5.8 Interrupt Request 5.9 General Reset 6 Application 6.1 Checksum Generation and Checking 6.1.1 Generation 6.1.2 Checking 6.2 Modem Performance 6.3 Modem Timing Information 6.4 TX Timing 6.4.1 TX More Than One Message, SYNC Before Every Message, TX Check-2 TX More Than One Message, TX Checksum Not Enabled 6.4.3 TX One Message, TX Checksum Enabled 6.4.4 TX One Message, TX Checksum Not Enabled 6.5 RX Timing 6.5.1 RX SYNC/SYNC Required Before Every Message, Rx Checksum Benabled 7 Performance Specifications 7.1 Electrical Specifications 7.1.1 Absolute Maximum Limits 7.1.2 Operating Characteristics 7.1.4 Timing                                                                                                                                                                                                                                                                                                                                                                    |    | 5.5 TX Data Buffer "Write to TX Data Buffer" | 10   |

| 5.8 Interrupt Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    | 5.6 SYNC Program "Write to SYNC Program"     | 10   |

| 5.9 General Reset  6 Application  6.1 Checksum Generation and Checking  6.1.1 Generation  6.1.2 Checking  6.2 Modem Performance  6.3 Modem Timing Information  6.4 TX Timing  6.4.1 TX More Than One Message, SYNC Before Every Message, TX Checksum Not Enabled  6.4.2 TX More Than One Message, TX Checksum Not Enabled  6.4.3 TX One Message, TX Checksum Enabled  6.4.4 TX One Message, TX Checksum Not Enabled  6.5 RX Timing  6.5.1 RX SYNC/SYNC Required Before Every Message, Rx Checksum Benabled  7 Performance Specifications  7.1 Electrical Specifications  7.1.1 Absolute Maximum Limits  7.1.2 Operating Limits  7.1.3 Operating Characteristics  7.1.4 Timing                                                                                                                                                                                                                                                                                                                                                      |    | 5.7 Read Status Register                     | 10   |

| 6.1 Checksum Generation and Checking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    | 5.8 Interrupt Request                        | 11   |

| 6.1 Checksum Generation and Checking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    | 5.9 General Reset                            | 11   |

| 6.1 Checksum Generation and Checking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6  | Application                                  | 12   |

| 6.1.1 Generation 6.1.2 Checking 6.2 Modem Performance 6.3 Modem Timing Information 6.4 TX Timing 6.4.1 TX More Than One Message, SYNC Before Every Message, TX Che 6.4.2 TX More Than One Message, TX Checksum Not Enabled 6.4.3 TX One Message, TX Checksum Enabled 6.4.4 TX One Message, TX Checksum Not Enabled 6.5 RX Timing 6.5.1 RX SYNC/SYNC Required Before Every Message, Rx Checksum Benabled 7 Performance Specifications 7.1 Electrical Specifications 7.1.1 Absolute Maximum Limits 7.1.2 Operating Limits 7.1.3 Operating Characteristics 7.1.4 Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    | ••                                           |      |

| 6.2 Modem Performance 6.3 Modem Timing Information 6.4 TX Timing 6.4.1 TX More Than One Message, SYNC Before Every Message, TX Che 6.4.2 TX More Than One Message, TX Checksum Not Enabled 6.4.3 TX One Message, TX Checksum Enabled 6.4.4 TX One Message, TX Checksum Not Enabled 6.5 RX Timing 6.5.1 RX SYNC/SYNC Required Before Every Message, Rx Checksum I 6.5.2 RX Additional Data Follows Initial Address (6 Data & 2 Checksum B Enabled 7 Performance Specifications 7.1 Electrical Specifications 7.1.1 Absolute Maximum Limits 7.1.2 Operating Limits 7.1.3 Operating Characteristics 7.1.4 Timing                                                                                                                                                                                                                                                                                                                                                                                                                      |    | Č                                            |      |

| 6.3 Modem Timing Information 6.4 TX Timing 6.4.1 TX More Than One Message, SYNC Before Every Message, TX Ch 6.4.2 TX More Than One Message, TX Checksum Not Enabled 6.4.3 TX One Message, TX Checksum Enabled 6.4.4 TX One Message, TX Checksum Not Enabled 6.5 RX Timing 6.5.1 RX SYNC/SYNC Required Before Every Message, Rx Checksum Not Enabled 6.5.2 RX Additional Data Follows Initial Address (6 Data & 2 Checksum Benabled 7 Performance Specifications 7.1 Electrical Specifications 7.1.1 Absolute Maximum Limits 7.1.2 Operating Limits 7.1.3 Operating Characteristics 7.1.4 Timing                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | 6.1.2 Checking                               | 12   |

| 6.4 TX Timing  6.4.1 TX More Than One Message, SYNC Before Every Message, TX Ch 6.4.2 TX More Than One Message, TX Checksum Not Enabled. 6.4.3 TX One Message, TX Checksum Enabled 6.4.4 TX One Message, TX Checksum Not Enabled. 6.5 RX Timing. 6.5.1 RX SYNC/SYNC Required Before Every Message, Rx Checksum I 6.5.2 RX Additional Data Follows Initial Address (6 Data & 2 Checksum B Enabled.  7 Performance Specifications. 7.1 Electrical Specifications. 7.1.1 Absolute Maximum Limits. 7.1.2 Operating Limits. 7.1.3 Operating Characteristics. 7.1.4 Timing.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    | 6.2 Modem Performance                        | 12   |

| 6.4.1 TX More Than One Message, SYNC Before Every Message, TX Che 6.4.2 TX More Than One Message, TX Checksum Not Enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | 6.3 Modem Timing Information                 | 13   |

| 6.4.2 TX More Than One Message, TX Checksum Not Enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | 6.4 TX Timing                                | 14   |

| 6.4.3 TX One Message, TX Checksum Enabled 6.4.4 TX One Message, TX Checksum Not Enabled 6.5 RX Timing 6.5.1 RX SYNC/SYNC Required Before Every Message, Rx Checksum I 6.5.2 RX Additional Data Follows Initial Address (6 Data & 2 Checksum B Enabled 7 Performance Specifications 7.1 Electrical Specifications 7.1.1 Absolute Maximum Limits 7.1.2 Operating Limits 7.1.3 Operating Characteristics 7.1.4 Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |                                              |      |

| 6.4.4 TX One Message, TX Checksum Not Enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    | 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2      |      |

| 6.5 RX Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    | 3 ,                                          |      |

| 6.5.1 RX SYNC/SYNC Required Before Every Message, Rx Checksum I 6.5.2 RX Additional Data Follows Initial Address (6 Data & 2 Checksum B Enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | -                                            |      |

| 6.5.2 RX Additional Data Follows Initial Address (6 Data & 2 Checksum B Enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | •                                            | 16   |

| Fnabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | , , , , , , , , , , , , , , , , , , , ,      |      |

| 7.1 Electrical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |                                              |      |

| 7.1.1 Absolute Maximum Limits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7  | Performance Specifications                   | 17   |

| 7.1.2 Operating Limits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | 7.1 Electrical Specifications                | 17   |

| 7.1.3 Operating Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | 7.1.1 Absolute Maximum Limits                | 17   |

| 7.1.4 Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    | 1 3                                          |      |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | , ,                                          |      |

| 7.2 Packages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    | · ·                                          |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | 7.2 Packages                                 | 21   |

MXCOM, Inc. reserves the right to change specifications at any time without notice.

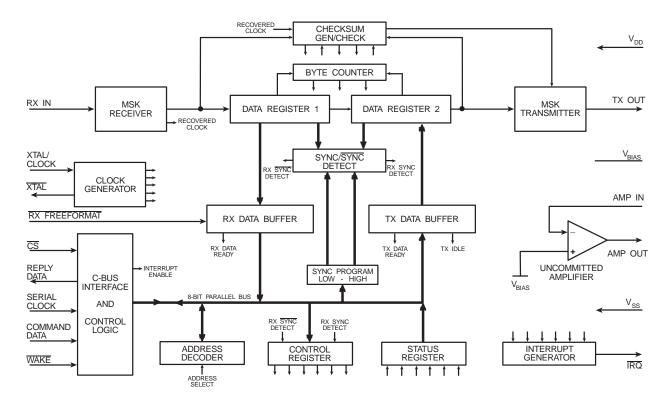

## 1 Block Diagram

Figure 1: Block Diagram

## 2 Signal List

| Pin | Signal            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Xtal              | This is the output of the on-chip clock oscillator. External components are required at this output when a Xtal is used. See Figure 2. Inset                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2   | Xtal/Clock        | This is the input to the on-chip clock oscillator inverter. A Xtal or externally derived clock should be connected here. See Figure 2. Inset                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3   | IRQ               | The output of this pin indicates an interrupt condition to the microcontroller by going to a logic "0". This is a "wire-or-able" output that enables the connection of up to 8 peripherals to 1 interrupt port on the microcontroller. This pin is an opendrain output, and therefore has a low impedance pulldown to logic "0" when active and a high impedance when inactive. The conditions that cause interrupts are indicted in the Status Register and are shown in Table 2. The system $\overline{\mbox{IRQ}}$ line requires a pull-up resistor to $\mbox{V}_{\mbox{DD}}$ . |

| 4   | N/C               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5   | N/C               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6   | RX Freeformat     | When this input is logic "0" in the RX Mode, it allows received data to be read from the RX Data Buffer via the Reply Data line without having to achieve byte synchronization (SYNC/SYNC) first. Data will continue to be available after this input goes to a logic "1" until either a SYNC or SYNC Prime Bit is set or the modem is set to TX Mode. When held at a logic "1" the modem operates                                                                                                                                                                                 |

|     |                   | normally. This pin has an internal $1M\Omega$ pull-up resistor. <b>Note</b> : If this input is held at a logic "0" in the TX Mode, the RX Data Ready bit in the Status Register may occasionally be set, but not cause an interrupt. If this input is a logic "0" when going into the RX Mode, and RX Data Ready interrupt may be generated immediately (in this case the first byte of RX data should be ignored).                                                                                                                                                                |

| 7   | V <sub>BIAS</sub> | The internal circuitry bias line, this is held at $V_{DD}/2$ . This pin must be decoupled to $V_{SS}$ by capacitor C3. See Figure 2.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8   | Amp In            | The inverting input to the on-chip uncommitted amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9   | Amp Out           | The output of the on-chip uncommitted amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10  | RX In             | This is the 1200 baud, 1200Hz/1800Hz received MSK signal input. The input signal to this pin must be AC coupled via capacitor C4. See Figure 2.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 11  | N/C               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12  | V <sub>SS</sub>   | Negative Supply (GND)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 13  | TX Out            | This is the 1200 baud, 1200Hz/1800Hz MSK TX output. When not transmitting data the output impedance of this pin is high. On power-up this output can be any level. A General Reset command is required to ensure that this output attains V <sub>BIAS</sub> initially.                                                                                                                                                                                                                                                                                                             |

| 14  | N/C               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 15  | N/C               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 16  | N/C               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 17  | Reply Data        | This is the C-BUS serial data output to the microcontroller. The transmission of Reply Data bytes is synchronized to the Serial Clock under the $\overline{CS}$ input. This 3-state output is held high impedance when not sending data to the microcontroller. See Section 6 and Section 7.1.4.                                                                                                                                                                                                                                                                                   |

| 18  | N/C               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 19  | CS                | Chip Select. This is the 'C-BUS' data loading control function. This input is provided by the microcontroller. Data transfer sequences are initiated, completed or aborted by the $\overline{CS}$ signal. See Section 6 and Section 7.1.4.                                                                                                                                                                                                                                                                                                                                         |

| 20  | Command Data      | This is the 'C-BUS' serial data input from the microcontroller. Data is loaded to this device in 8-bit bytes, MSB (bit 7) first and LSB (bit 0) last, synchronized to the Serial Clock. See Section 6 and Section 7.1.4.                                                                                                                                                                                                                                                                                                                                                           |

| Pin | Signal         | Description                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21  | Serial Clock   | This is the 'C-BUS' serial Clock input. This clock, produced by the microcontroller, is used for transfer timing of commands and data to and from the MSK Modem. See Section 6 and Section 7.1.4.                                                                                                                                                                                                                                   |

| 22  | Address Select | This pin enables two MX809s to be used on the same C-BUS, providing full-duplex operation. When at a logic "1" Address/Command bytes (with the exception of a General Reset) must have bit 3 set to a logic "1" to address this device. See Table 5 and Table 6.                                                                                                                                                                    |

| 23  | Wake           | This input can be used to reactivate the MX809 from Powersave. The device will be in Powersave when both this pin and bit 2 of the Control Register are set to logic "1". Recovery from Powersave is achieved by putting either the Wake pin or the Powersave bit in the Control Register to logic "0". This allows MX809 activation by the microcontroller or an external signal, such as R.S.S.I. or Carrier Detect. See Table 3. |

| 24  | $V_{DD}$       | Positive supply. A single +5.0V power supply is required. Levels and voltages within the MSK Modem are dependent upon this supply.                                                                                                                                                                                                                                                                                                  |

Table 1: Signal List

| TX Idle                                                            | RX Data Ready | TX Data Ready  |  |  |  |

|--------------------------------------------------------------------|---------------|----------------|--|--|--|

| RX SYNC Detect                                                     |               | RX Sync Detect |  |  |  |

| Interrupt outputs can be disabled by bit 3 of the Control Register |               |                |  |  |  |

Table 2: IRQ Conditions

| Powersave (CR bit 2) | Wake | MX809 Condition |

|----------------------|------|-----------------|

| 1                    | 1    | Powersave       |

| 0                    | 1    | Enabled         |

| 1                    | 0    | Enabled         |

| 0                    | 0    | Enabled         |

Table 3: Wake and Powersave Conditions

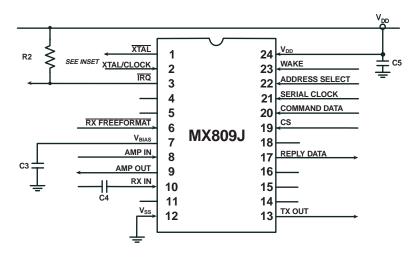

## 3 External Components

Figure 2: Recommended External Components

| Component | Notes | Value              | Tolerance |

|-----------|-------|--------------------|-----------|

| R1        |       | $1.0 { m M}\Omega$ | ±10%      |

| R2        |       | 22.0KΩ             | ±10%      |

| C1        | 1     | 33pF               | ±20%      |

| C2        | 1     | 33pF               | ±20%      |

| C3        |       | 1.0μF              | ±20%      |

| C4        |       | 0.1μF              | ±20%      |

| C5        |       | 1.0μF              | ±20%      |

| X1        | 1     | 4.032MHz           |           |

**Table 4: Recommended External Components**

## **Recommended External Component Notes:**

Xtal circuit capacitors C1 (CD) and C2 (CG) shown in Inset 2 are recommended in accordance with MX-COM's Crystal Oscillator Application Note.

## 4 General Description

The MX809 is an intelligent, half-duplex 1200-baud MSK Modem, which operates under C-BUS control. This modem provides software selectable checksum generation and error checking in accordance with MPT1327. In TX Mode the MX809 will:

- 1. a) Accept from the host and transmit 8-bit bytes of data as instructed (preamble, sync, address, and data), or

- b) Internally calculate and inset a 2 byte checksum based on the preceding 6 bytes of data, or

- c) Disable the internal checksum generator and continuously transmit the data supplied.

- Transmit 1 hang-bit and go to TX idle when all loaded data bytes have been transmitted.

#### In RX Mode the MX809 will:

- 1. Detect and carry out bit synchronization within 16 bits.

- a) Search and detect the user-programmed Sync (or its opposite logic sense) Word and carry out frame synchronization. Data will then be output in 8-bit bytes via the RX Data Buffer.

- b) Use the received checksum to calculate the presence of any errors, setting the Status Register accordingly.

- 3. Make the incoming data directly available via the RX Data Buffer (RX Freeformat), overriding the synchronization requirements.

RX input timing is achieved by recovering an RX clock from the incoming data stream. Output tones are timed to the internally generated TX clock. Filter, register clocks, and transmit MSK tone frequencies are derived internally from the external Xtal or clock pulse input.

A 4.032MHz Xtal or clock input is required for compliance with the MPT1327 Signaling Specification. Note: All information contained in this data bulletin is specified using a 4.032MHz Xtal, 1200bps baud rate, with Mark and Space frequencies of 1200Hz and 1800Hz. The MX809 has a non-committed amplifier on-chip for general applications in the DBS 800 series.

## 5 Controlling Protocol

Control of the functions within the MX809 MSK Modem is by a group of Address/Commands and appended data instructions from the system microcontroller. Two separate MSK Modems can be addressed. The use of these A/Cs is detailed in the following paragraphs and tables.

| Command Assignment        |     | Address/Command<br>Binary |   | Command Data                                      |

|---------------------------|-----|---------------------------|---|---------------------------------------------------|

|                           | HEX | MSB LSB                   |   |                                                   |

| General Reset             | 01  | 0000001                   |   | Control Register bits set to logic "0"            |

| Write to Control Register | 40  | 01000000                  | + | 1 byte instruction to Control Register            |

| Read Status Register      | 41  | 01000001                  | + | 1 byte reply from Status Register                 |

| Read RX Data Buffer       | 42  | 01000010                  | + | 1 byte of data from RX Data Buffer                |

| Write to TX Data Buffer   | 43  | 01000011                  | + | 1 byte of data to TX Data Buffer                  |

| Write to SYNC Program     | 44  | 01000100                  | + | 2 bytes of SYNC Word to SYNC<br>Program. Register |

Table 5: Modem No. 1 C-BUS Address/Commands – (Address Select input at a logic "0")

#### 5.1 Address/Commands

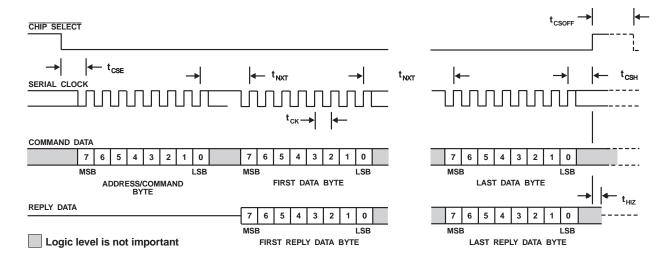

Instructions and data transactions to and from the MX809 consist of an Address/Command (A/C) byte followed by either further instructions or data, or a Status or RX Data Reply.

Control and configuration is by writing instructions from the microcontroller to the Control Register [40<sub>H</sub> (48<sub>H</sub>)].

Reporting of the MX809 configuration is by reading the Status Register [41<sub>H</sub> (49<sub>H</sub>)]. Instructions and data are transferred via C-BUS in accordance with the timing information given in Figure 11.

Data to be transmitted as MSK is sent to the TX Data Buffer via the Command Data line. Received data is read from the RX Data buffer via the Reply Data line.

Instructions and data transactions to and from this device are preceded by the relevant A/C.

C-BUS allocations for the MX809 are shown in Table 5 and Table 6.

| Command Assignment        |     | Address/Command<br>Binary |   | Command Data                                     |

|---------------------------|-----|---------------------------|---|--------------------------------------------------|

|                           | HEX | MSB LSB                   |   |                                                  |

| General Reset             | 01  | 0000001                   |   | Control Register bits set to logic "0"           |

| Write to Control Register | 48  | 01001000                  | + | 1 byte instruction to Control Register           |

| Read Status Register      | 49  | 01001001                  | + | 1 byte reply from Status Register                |

| Read RX Data Buffer       | 4A  | 01001010                  | + | 1 byte of data from RX Data Buffer               |

| Write to TX Data Buffer   | 4B  | 01001011                  | + | 1 byte of data to TX Data Buffer                 |

| Write to SYNC Program     | 4C  | 01001100                  | + | 2 bytes of SYNC Word to SYNC<br>Program Register |

Table 6: Modem No. 2 C-BUS Address/Commands – (Address Select input at a logic "1")

## 5.2 Address Select

This input allows 2 MSK Modems on the same BUS, using the correct addressing.

When operating in a system using 2 MSK Modems, one MSK Modem is designated No. 1 and requires its Address Select input to be held at a logic "0". The second Modem (No. 2) requires its Address select input to be held at logic "1".

All C-BUS transactions with Modem 1 will use Address/Command allocations  $40_H$  to  $44_H$  (Table 5) and transactions with Modem 2 will use  $48_H$  to  $4C_H$  (Table 6).

For explanation purposes, further descriptions of MX809 MSK Modem internal register functions will deal primarily with MSK Modem No. 1 (Address Select at logic "0").

## 5.3 Write to Control Register

This "Write Only" register directs the Modem's operation.

**SYNC**: When set, this bit enables **SYNC** Word detection. It is cleared on a successful **SYNC** Word detection.

**SYNC Prime:** When set, this bit enables SYNC Word detection. It is cleared on a successful SYNC Word detection.

**Interrupt Enable:** When set, this bit allows interrupts to be output by the MX809 on the  $\overline{|RQ|}$  line.

**Powersave:** Used in conjunction with the Wake input (see Section 2) to control the Powersave state of the MX809.

Checksum Enable: When set:

In TX: A 2-byte checksum is generated and transmitted after every 6 bytes transmitted.

**In RX**: After every 8 received bytes (6 information + 2 checksum) the checksum word is checked. If the checksum is correct, the RX Checksum True bit in the Status Register is set to a logic "1". When this bit is a logic "0" no checksum are generated or checked.

**Note:** Checksum operation is inhibited during the SYNC/SYNC search period.

| Setting | Control bits      |

|---------|-------------------|

| MSB     | Transmitter first |

| Bit 7   | Not Used          |

|         | Set to "0"        |

| 6       | Not Used          |

|         | Set to "0"        |

| 5       | SYNC Prime        |

| 0       |                   |

| 1       | Primed            |

| 4       | SYNC Prime        |

| 0       |                   |

| 1       | Primed            |

| 3       | Interrupt Enable  |

| 0       | Disable           |

| 1       | Enable            |

| 2       | Powersave         |

| 0       | Normal Operation  |

| 1       | Powersave         |

| 1       | Checksum Enable   |

| 0       | Disable           |

| 1       | Enable            |

| 0       | RX/TX Mode        |

| 0       | RX                |

| 1       | TX                |

**Table 7: Control Register**

## 5.4 RX Data buffer -- "Read RX Data Buffer"

This "Read Only" register contains the last byte of data received from the Data Register. Data is received Bit 7 (MSB) first.

| MSB            |   |   |   |   |   |   | LSB |

|----------------|---|---|---|---|---|---|-----|

| 7              | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

| RX Data Buffer |   |   |   |   |   |   |     |

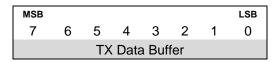

## 5.5 TX Data Buffer -- "Write to TX Data Buffer"

This "Write Only" register contains the next byte of data to be transmitted. Bit 7 (MSB) is transmitted first.

## 5.6 SYNC Program -- "Write to SYNC Program"

This "Write Only" register is loaded with the required SYNC word. This word (or its opposite logic sense, SYNC) is compared with the received synchronization word. If the required SYNC Word is less that 16bits, the remaining bits must be programmed as preamble (10101010...etc). Bit 15 (MSB) is loaded first.

| MSB       |    | Byte 1 |    |    |    |   |   |   |      |       | Byte 2 |   |   |   | LSB |

|-----------|----|--------|----|----|----|---|---|---|------|-------|--------|---|---|---|-----|

| 15        | 14 | 13     | 12 | 11 | 10 | 9 | 8 | 7 | 6    | 5     | 4      | 3 | 2 | 1 | 0   |

| SYNC High |    |        |    |    |    |   |   |   | SYNC | C Low |        |   |   |   |     |

## 5.7 Read Status Register

This "Read Only" register indicated the source of MX809 interrupts (IRQs).

**RX SYNC** Detect: This is set and an Interrupt is generated when the correct SYNC Word is detected (if SYNC Prime is set).

It is cleared by (1) reading the Status Register, and (2) setting  $\overline{RX}/TX$  to logic "1".

RX SYNC Detect: This is set and an Interrupt is generated when the correct SYNC Word is detected (if SYNC Prime is set).

It is cleared by (1) reading the Status Register, and (2) setting  $\overline{RX}/TX$  to logic "1".

TX Idle: This is set and an Interrupt is generated when all loaded TX data and 1 "hang-bit" have been transmitted.

It is cleared by (1) writing to the TX Data Buffer, and (2) setting RX/TX to logic "0".

TX Data Ready: This is set and an Interrupt generated indicating that a byte of data should be written to the TX Data Buffer.

It is cleared by (1) reading the Status Register and writing a byte of data to the TX Data Buffer, and (2) setting  $\overline{RX}/TX$  to logic "0".

RX Data Ready: When this is set and an Interrupt generated, it indicates that the RX Data Buffer is full, and that a byte of data is to be read from the RX Data buffer. This must be read within 8 bit periods.

It is cleared by (1) reading the Status Register and the RX Data buffer, and (2) setting the RX/TX to logic "1"/

RX Checksum True: This is set and an Interrupt is generated by a successful comparison of the received and self-generated checksums.

It is cleared by (1) reading the Status Register and the RX Data Buffer, and (2) RX/TX being taken to logic "1"

| Reading | Status Bits      |

|---------|------------------|

| MSB     | Received First   |

| Bit 7   | Undefined        |

| 0       | "0" or           |

| 1       | "1"              |

| 6       | Undefined        |

| 0       | "0" or           |

| 1       | "1"              |

| 5       | RX SYNC Detect   |

| 0       |                  |

| 1       | SYNC             |

| 4       | RX SYNC Detect   |

| 0       |                  |

| 1       | SYNC             |

| 3       | TX Idle          |

| 0       |                  |

| 1       | Idle             |

| 2       | TX Data Ready    |

| 0       |                  |

| 1       | TX Date Ready    |

| 1       | RX Checksum True |

| 0       |                  |

| 1       | True             |

| 0       | RX Data Ready    |

| 0       |                  |

| 1       | RX Data Ready    |

**Table 8: Status Register**

## 5.8 Interrupt Request

The conditions that cause interrupts to be output (if enabled by the Control Register) from the MX809 are:

TX Idle

TX Data Ready

RX SYNC Detect

RX Data Ready

RX SYNC Detect

The Status Register should be read to find the cause of the interrupt. Interrupts are cleared by (1) reading the Status Register, or (2) changing the state of the  $\overline{RX}/TX$  bit.

## 5.9 General Reset

Upon power-up, the bits in the MX809 Mode register and buffer will be random (either "0" or "1"). The General Reset command (01<sub>H</sub>) will "reset" all microcircuits in the C-BUS and had the following effect on the MX809.

All bits in the Control Register will be set to logic "0". The Tx Out output will be set to V<sub>BIAS</sub>.

**Note**: The Status register, RX Data Buffer, TX Data Buffer, and SYNC Program register are not affected by the General Reset Command.

## 6 Application

## 6.1 Checksum Generation and Checking

#### 6.1.1 Generation

The checksum generator takes the 48 bits from the 6 bytes loaded into the TX Data Buffer and divides them into modulo-2 by the generating polynomial:

$$x^{15} + x^{14} + x^{13} + x^{11} + x^{4} + x^{2} + x^{1}$$

It then takes the 15-bit remainder from the polynomial divider, inverts the last bit and appends an EVEN parity bit generated from the initial 48 bits and the 15 bit remainder (with the last bit inverted). This 16 bit word is used as the "Checksum".

### 6.1.2 Checking

The checksum checker does two things:

1. It takes the first 63 bits of a received message, inverts bit 63, and divides them modulo-2 by the generating polynomial:

$$x^{15} + x^{14} + x^{13} + x^{11} + x^4 + x^2 + x^1$$

- 2. The 15 bits remaining in the polynomial divider are checked to make sure that they are all zero.

- It generates an even parity bit from the first 63 bits of a received message and compares this bit with the received parity (bit 64).

- If the 15 bits in the polynomial divider are all zero and the two parity bits are equal, then the RX Checksum True (Status Register bit 1) is set.

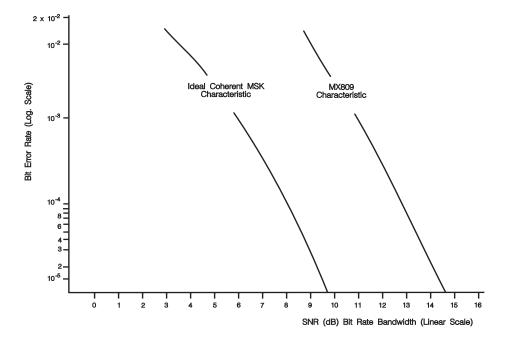

### 6.2 Modem Performance

Figure 3: Bit Error Rate vs. Signal-to-Noise Ratio

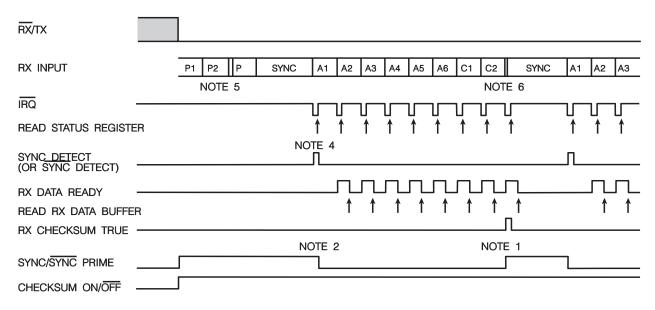

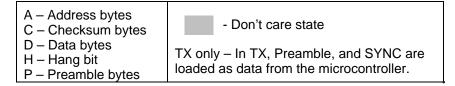

## 6.3 Modem Timing Information

Figure 4: Modem Timing

- 1. The SYNC and SYNC detector searches the incoming bit stream starting at the end of the byte in which SYNC/SYNC Prime was set.

- 2. After detection of a SYNC/SYNC word, the SYNC/SYNC Prime bits automatically go low (control bits 5 and 6: detector off.

- 3. The checksum checker is inhibited during the time SYNC/SYNC search is operating.

- 4. The Status Register will indicate whether SYNC or SYNC was detected here.

- 5. Any number of preamble bits can occur here.

- 6. Any number of bits can occur here.

- 7. RX Freeformat set high.

## 6.4 TX Timing

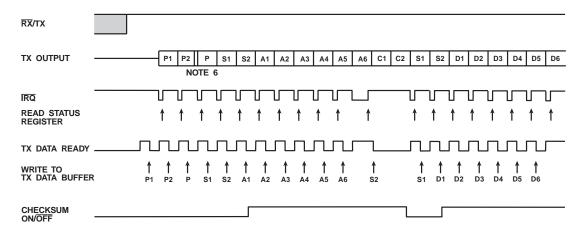

## 6.4.1 TX More Than One Message, SYNC Before Every Message, TX Checksum Enabled

Figure 5: TX More Than One Message, SYNC Before Every Message, TX Checksum Enabled

#### Notes:

- 1. Preamble and SYNC bytes are loaded as data from the microcontroller.

- 2. The TX output will be held at bias level when no data is being transmitted.

- 3. TX byte synchronization is established by loading of the first preamble byte from the microcontroller.

- 4. Checksum must be turned off during preamble and SYNC words.

- 5. When  $\overline{RX}/TX$  is low, TX output is at bias.

- 6. Any number of preamble bytes can occur here.

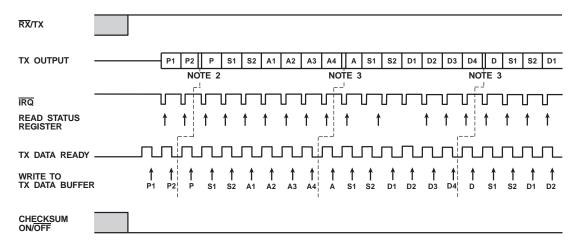

## 6.4.2 TX More Than One Message, TX Checksum Not Enabled.

Figure 6: TX More Than One Message, TX Checksum Not Enabled.

- 1. Preamble, SYNC words and checksums are supplied by the microcontroller in this format as data bytes.

- 2. Any number of preamble bytes can occur here.

- 3. Any number of address/data bytes can occur here.

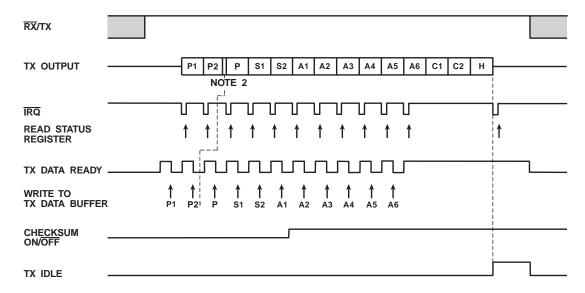

### 6.4.3 TX One Message, TX Checksum Enabled

Figure 7: TX One Message, TX Checksum Enabled

#### Notes:

- H is the "Hangover bit" (Logic1) appended to the transmitted message before transmission is terminated.

- 2. Any number of preamble bytes can occur here.

- 3. Transmission terminates after C1, C2, and H. Termination occurs when no further data bytes are written to the TX Data Buffer.

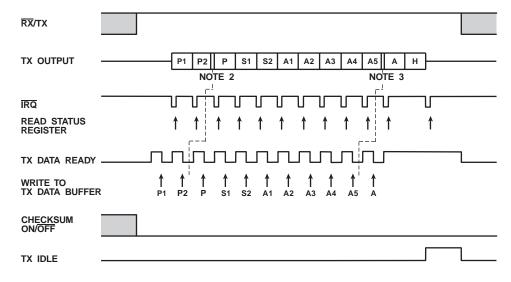

#### 6.4.4 TX One Message, TX Checksum Not Enabled.

Figure 8: TX One Message, TX Checksum Not Enabled

- 1. H is the "Hangover bit" (Logic1) appended to the transmitted message before transmission is terminated.

- Any number of preamble bytes can occur here.

- 3. Any number of address/data bytes can occur here.

- Transmission terminates when no further data bytes are loaded into the TX Data Buffer.

## 6.5 RX Timing

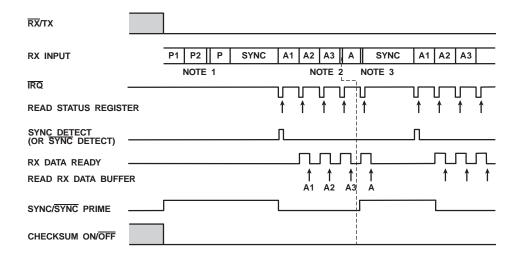

## 6.5.1 RX SYNC/SYNC Required Before Every Message, Rx Checksum Not Enabled

Figure 9: RX SYNC/SYNC Required Before Every Message, RX Checksum not Enabled

#### Notes:

- 1. Any number of preamble bits can occur here.

- 2. Any number of address/data bytes can occur here.

- 3. Any number of bits can occur here

- 4. RX Freeformat set high.

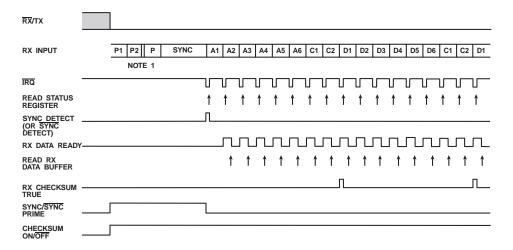

## 6.5.2 RX Additional Data Follows Initial Address (6 Data & 2 Checksum Bytes) Data, RX checksum Enabled

Figure 10: RX Additional Data Follows Initial Address (6 Data & 2 Checksum Bytes) Data , RX Checksum Enabled

- 1. Any number of preamble bits can occur here.

- 2. RX Freeformat set high.

## 7 Performance Specifications

## 7.1 Electrical Specifications

## 7.1.1 Absolute Maximum Limits

Exceeding these maximum ratings can result in damage to the device.

| General                                                      | Notes | Min. | Тур. | Max.           | Units            |

|--------------------------------------------------------------|-------|------|------|----------------|------------------|

| Supply (V <sub>DD</sub> -V <sub>SS</sub> )                   |       | -0.3 |      | 7.0            | V                |

| Voltage on any pin to V <sub>SS</sub>                        |       | -0.3 |      | $V_{DD} + 0.3$ | V                |

| Current                                                      |       |      |      |                |                  |

| $V_{DD}$                                                     |       | -30  |      | 30             | mA               |

| V <sub>SS</sub>                                              |       | -30  |      | 30             | mA               |

| Any other pin                                                |       | -20  |      | 20             | mA               |

| J / LH Packages                                              |       |      |      |                |                  |

| Total allowable Power dissipation at T <sub>AMB</sub> = 25°C |       |      |      | 800            | mW               |

| Derating above 25°C                                          |       |      | 10   |                | mW/°C above 25°C |

| Operating Temperature                                        |       | -40  |      | 85             | °C               |